预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 13 电子行业报告

探测器芯片同样种类很多,原理上基于光电效应(可分为内光电效应和外光电 效应),通信领域的探测器细分来看可归为基于内光电效应的光生伏特探测器,根 据放大与否,可进一步分为非放大的 PIN(二级管探测器)和包含放大的 APD(雪 崩二级管探测器)两种。前者的灵敏度相对较低,但噪声小,工作电压低,成本低, 适用于中短距离的光通信传输。APD 在灵敏度以及接收距离上优于 PIN,但成本 高于 PIN。PIN 的工作流程分为两步,一是材料在入射光照射下产生光生载流子, 二是光电流与外围电路间的相互作用并输出电信号。与 PIN 相较,APD 较之 PIN 探测器多了一个雪崩倍增区域,加上一个较高的反向偏置电压后,利用雪崩击穿效 应,可在 APD 中获得一个很大的内部电流增益,从而实现更高的灵敏度等优势。工艺流程复杂,涉及诸多精密加工环节,技术壁垒高。以制造一颗 25G DFB 激光器芯片为例,若不涵盖封装测试环节,大致可分为 9 大部分,整个生产工序 超过 280 道,每道生产工序包括工艺设计都将影响产品最终的性能和可靠性。外延环节对设计及生产工艺的要求高,是当前国内厂商与海外头部厂商的主 要差距所在。经验积累包括生产过程的良率爬坡都需要较长时间,因而先发优势明 显,是厂商竞争优势及技术实力的核心体现,1)从工艺角度:需对材料厚度、比 例、电学掺杂、缺线控制等参数进行精确控制。以 25G DFB 芯片为例,有源层包 含了 20~30 层的量子阱结构,每层量子阱的厚度在 4~10nm 不等,工艺上要求 对每层量子阱实现埃米级(0.1nm)控制,厚度精度误差小于 0.2nm。

除了厚度 外,每层量子阱的材料比例误差也会造成量子阱发光波长误差、量子阱各层间的应 力误差均会影响产品最终的性能与可靠性;2)从设计的角度:须要对相关参数进 行精细设计以实现所需性能,这就要求激光器芯片厂商利用理论仿真指导外延技 术的开发,通过模拟仿真量子阱结构、理论计算晶圆光电特性,在生产前预判晶圆 性能趋势,便于进行有源区晶圆外延工艺参数匹配调试,有效缩短开发周期;3) 从生产良率的角度,生产难度高,需要较长时间的经验积累和良率爬坡过程,先发 优势明显。高端产品上,国内厂商与海外头部厂商在各方面性能上仍有较大差距。光模块速率加速提升,驱动激光器芯片更新迭代升级。以数通领域为例,流量 高速增长、光模块单位速率成本下降、交换机芯片升级扩容等多种因素均是驱动光 模块速率升级的重要因素,基本 3~5 年完成一次光模块速率的升级迭代。光模块 速率提升主要有三种途径:1)提升激光器芯片的速率(波特率),2)提升光模块 的通道数,3)较之传统的 NRZ 调制,使用更高阶的信号调制技术,如 PAM4 和相干调制。以上三种方式的具体选择涉及到综合权衡技术难度、成本、光模块体积、 散热等方面因素。从激光器芯片速率升级的角度,数通领域从 40G 光模块中常用 的 10G 波特率的 VCSEL/DFB 芯片,到 100G 光模块中常用的 25G 波特率的 VCSEL/DFB 芯片,再到高端光模块如 400G 中常用的 50G 波特率的 EML 芯片, 呈现明显的激光器芯片更新迭代过程,包括随着未来硅光的进一步推进,大功率激 光器芯片的重要性也将进一步提升。

、

、

标签: 电子行业报告

相关文章

预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 13 电子行业报告

受下游需求影响及我国设备商国产替代加速,2024年我国引线键合机进口市场空间约6.18亿美元,仍显著低于 2021年高峰期进口市场空间的15.9亿美元...

2025-04-11 42 电子行业报告

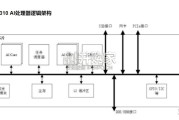

满足飞速发展的深度神经网络对芯片算力的需求,昇腾AI处理器本质上是一个SoC(System on Chip)。以昇腾310 AI 处理器为例,主要可以...

2025-03-29 75 电子行业报告

最新留言