预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 13 电子行业报告

异构多核 SoC 成传统大规模集成电路主流趋势。随着先进工艺节点不断推进,芯片线宽缩小下单颗芯片可容纳 的晶体管数量不断提升,7nm 工艺节点下 80mm²裸片晶体管数量增长至近 70 亿个。传统大规模集成电路主流 趋势为异构多核 SoC,微处理器、模拟 IP、数字 IP、存储器等以同一种工艺制造方式被集成在单一芯片上,实 现芯片体积缩小及性能、可靠性的提高。 先进工艺节点下晶体管单位成本不断下降,但 IC 设计复杂度及设计成本不断提升。以先进工艺节点处于主流应 用时期设计成本为例,工艺节点为 28nm 时,单颗芯片设计成本约为 0.41 亿美元,而工艺节点为 7nm 时,设 计成本快速提升至 2.22 亿美元。即使工艺节点达到成熟应用时期,设计成本大幅度下降的前提下,相较同一应 用时期的上一代先进工艺节点,仍存在显著提升;此外,设计复杂度的提升也将对芯片良率产生影响,间接提高 了整体制造成本。Chiplet 将满足特定功能的裸片通过 die-to-die 内部互联技术,实现多个模块芯片与底层基础芯片的系统封装, 实现一种新形式的 IP 复用。基于裸片的 Chiplet 方案将传统 SoC 划分为多个单功能或多功能组合的芯粒,在一 个封装内通过基板互连成为一个完整的复杂功能芯片,是一种以裸片形式提供的硬核 IP。

在当前技术进展下,Chiplet 方案能够实现芯片设计复杂度及设计成本降低。IC 设计阶段将 SoC 按照不同功能 模块分解为多个芯粒,部分芯粒实现模块化设计并在不同芯片中重复使用,能够实现设计难度降低,且有利于后 续产品迭代,加速产品上市周期。 Chiplet 的运用也将大幅提高大型芯片良率的同时降低芯片制造成本。高性能计算等领域巨大运算需求推动逻辑 芯片运算核心数量上升,配套 SRAM 容量、I/O 数量随之提升。Chiplet 设计分割不同功能模块进行独立制造, 提升良率的同时降低不良率造成的额外制造成本。根据 Linley 测算,7nm 方案下 Chiplet 良率改善 0.8x,制造成 本降低至传统方案的 0.87 倍。我们认为,Chiplet 的实现需要架构设计与先进封装两侧的共同作用。架构侧为实现“分”的关键,需要考虑访 问频率、缓存一致性等;先进封装侧为“合”的关键,功耗、散热、整体成本为主要影响因素。目前主流架构设计方案可分为两类:(1)基于功能划分多个 Chiplet,通过不同 Chiplet 组合封装,实现不同类型 产品,典型代表为 Lego、AMD Zen2/3;(2)单一 Chiplet 包含独立完整功能集合,通过多个 Chiplet 组合实现 性能线性增长,典型代表为 Apple M1 Ultra 及 Intel Sappire Rapids。苹果方案通过自研封装技术堆叠两颗 M1 Max 芯片,两颗芯片间具备超过 2.5TB/s 带宽且极低延时互联能力,使 M1 Ultra 获得两倍算力,同时在软件层 面将 M1 Ultra 作为完整芯片,从而不增加额外软件修改和调试负担。

标签: 电子行业报告

相关文章

预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 13 电子行业报告

受下游需求影响及我国设备商国产替代加速,2024年我国引线键合机进口市场空间约6.18亿美元,仍显著低于 2021年高峰期进口市场空间的15.9亿美元...

2025-04-11 42 电子行业报告

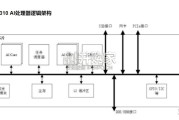

满足飞速发展的深度神经网络对芯片算力的需求,昇腾AI处理器本质上是一个SoC(System on Chip)。以昇腾310 AI 处理器为例,主要可以...

2025-03-29 75 电子行业报告

最新留言