预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 12 电子行业报告

缩短芯片间通信距离能够大幅度提升整个功能系统效率,SoC(Sytem on Chip)的方案将 不同芯片功能集成在一颗芯片上,使得芯片间通信在零级封装就已经完成,通信效率提升 到极大水平,因此我们看到过去几年在摩尔定律的引领下,芯片制程不断演进,从而使得 单芯片上晶体管数量大幅提升。但随着多年以来摩尔定律的推进,SoC 方案的发展在设计 和制造等方面都遇到了相当大的瓶颈: 1) 设计瓶颈,传统的 SoC 是将不同类型计算任务的计算单元设计在一块晶圆上,并且每 个计算单元都采用统一的工艺制程,导致 SoC 芯片上各个单元需要同步进行迭代,这 样不仅会使得系统重构风险高,同时也会使得芯片设计成本越来越高,根据行业经验 数据,设计一颗 28nm SoC 芯片成本约为 0.5 亿美金,7nm 需要 3 亿美金,5nm 需要 5 亿美金,3nm 则可能达到 15 亿美金。 2) 制造瓶颈,当前芯片工艺制程尺寸已走向极致(3nm 至 1nm),而 1nm 的宽度仅能容纳 2 个硅原子晶格,进一步微缩就将进入量子物理范畴,将面临量子隧穿效应等问题; 同时 SoC 挤进更多功能将导致芯片面积较大,从而导致良率难以提升,从行业经验数 据来看,面积 40*40mm 的良率只有 35.7%,面积 20*20mm 的良率可上升至 75.7%,面 积 10*10mm 的良率可提升至 94.2%;除此之外还存在光刻技术难以跟进、单芯片功耗 和散热问题越发突出、存储带宽难以跟进等问题,可见 SoC 制造难度正在加速上升。 制造难度的提升导致摩尔定律逐步开始失效,根据 IBS 的统计,芯片制程下降所带来 的制造成本下降幅度已经逐步收窄,16nm到10nm每10亿颗晶体管的成本可降低31%, 而从 7nm 到 5nm 仅降低 18%、从 5nm 到 3nm 仅降低 4%。

标签: 电子行业报告

相关文章

预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 12 电子行业报告

受下游需求影响及我国设备商国产替代加速,2024年我国引线键合机进口市场空间约6.18亿美元,仍显著低于 2021年高峰期进口市场空间的15.9亿美元...

2025-04-11 41 电子行业报告

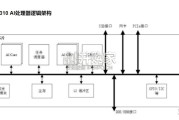

满足飞速发展的深度神经网络对芯片算力的需求,昇腾AI处理器本质上是一个SoC(System on Chip)。以昇腾310 AI 处理器为例,主要可以...

2025-03-29 75 电子行业报告

最新留言