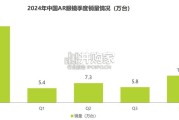

2024年,中国AR眼镜市场迎来发展高峰,更多品牌新品进入市场,并且AR眼镜在便携性、轻量化、功能性、技术性等方面均有显 著提升,更好地满足了消费者需...

2025-04-20 6 电子行业报告

EDA 可以降低芯片设计风险、减少试错成本。由于芯片产品一经制造就无法更改,其设计 的复杂度和高昂的制造和研发费用决定了需要通过 EDA 进行虚拟的设计、模拟和仿真,EDA 工 具在此过程中可用于:1)降低设计风险。芯片设计本身具有风险,需要大量验证流程和工作, EDA 能够将复杂物理问题用量化模型高度精确表述,在虚拟软件中模拟电路过程,再现芯片开 发过程中的各种效应,从而发现潜在设计缺陷和风险;2)减少试错成本。EDA 能够确保在逻辑 功能正确的前提下,模拟和分析得出特定半导体工艺在各种条件下性能、功耗、成本等的最优解, 解决多目标约束问题,减少试错成本;3)验证模型一致性,确保多个设计环节中芯片保持逻辑 功能一致。 EDA 工具技术的进步和应用一直以来是推动芯片设计成本保持在合理范围的重要方式,根 据加州大学圣迭戈分校 Andrew Kahng 教授在 2013 年的推测,2011 年设计一款消费级应用 处理器芯片的成本约 4000 万美元,如果不考虑 1993 年至 2009 年的 EDA 技术进步,相关设计 成本可能高达 77 亿美元,EDA 技术进步让设计效率提升近 200 倍。

EDA 工具可分类为:IC 设计软件、电子电路设计与仿真工具、PCB 设计软件、PLD 设计工 具等。1)IC 设计软件涵盖了设计输入、逻辑综合、布局布线、物理验证、模拟电路仿真器等子 工具,Synopsys、Cadence、Mentor Graphics 为全球主要的 IC 软件供应商;2)电子电路设 计与仿真工具主要是帮助设计人员通过模拟电路设计进行分析和改进优化,现有主流工具包括 SPICE、EWB 等;3)PCB 设计软件用于画板级电路图、布局布线和仿真,主流软件包括 Protel、 Cadence PSD 等;4)PLD 设计工具是一种由用户根据需要自行构造逻辑功能的数字集成电路, 主要厂商有 ALTERA 和 Xilinx。EDA 的出现和快速发展使得自顶向下的设计方法成为可能。自顶向下的设计方法即先定义 系统最高逻辑层次的功能模块,而后根据顶层模块的需求来定义子模块,然后逐层继续分解,最 终达到底层物理设计。设计过程包括从自然语言说明到 VHDL 的系统行为描述,从模块分解、 RTL 模型建立、门级电路生成到物理布线实现底层电路,抽象级别由高到低。

标签: 电子行业报告

相关文章

2024年,中国AR眼镜市场迎来发展高峰,更多品牌新品进入市场,并且AR眼镜在便携性、轻量化、功能性、技术性等方面均有显 著提升,更好地满足了消费者需...

2025-04-20 6 电子行业报告

预计 24 年电视全球零售额稳健增长,北美、西欧增速较快。据欧睿数据,预计 24 年电视全球零售额为 1180 亿美元,同比+0.6%,其中亚太/西欧...

2025-04-17 18 电子行业报告

受下游需求影响及我国设备商国产替代加速,2024年我国引线键合机进口市场空间约6.18亿美元,仍显著低于 2021年高峰期进口市场空间的15.9亿美元...

2025-04-11 42 电子行业报告

最新留言