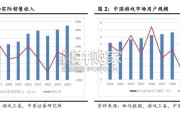

根据伽马数据和游戏工委联合发布的《中国游戏产业报告》数据,2024 年国内游戏市场规 模约 3257.83 亿元,同比增长 7.53%,用户规模约 6...

2025-04-18 12 TMT行业报告

半导体器件模型是 Spice 电路模拟的基础,是工艺和计算机技术的连接点之一。半导体器 件模型和用户工艺线紧密联系。在芯片设计之前,器件模型参数已由晶圆代工(Foundry) 公司通过 PDK 中的模型库提供给芯片设计人员。Spice 中包含电容、电感等模型,MOSFET 是其中最重要的模型。 半导体器件模型推动芯片制程向更高水平推进。70-80 年代,MOSFET 工艺由于低功耗, 高集成度成为主流,诞生大量 MOSFET 模型。90 年代,BSIM 逐步推广,代码量由数十行 上升为上万行。2010 年以来,基于 Verilog-A 语言的 FinFET 模型推动芯片制程不断向更高 水平推进,从而推动 EDA 行业不断向前发展。ASIC 芯片半定制设计方法激发设计需求:80 年代可编程逻辑器件迅速发展。ASIC 芯片可 分为全定制、半定制、可编程三类,半定制方法采用带有基本单元的母片或标准单元库中 的标准单元(门/微处理器/存储器等),系统设计师可以根据基本单元选择布线,而不需要了 解物理版图、加工工艺,就可以利用编程语言进行设计,EDA 市场由此逐步打开。单元库进一步提升设计的抽象化程度,使设计师能专注于系统设计。单元库提供预设的标 准单元。各类单元库包含了预先设计好的各种特性逻辑门,可以帮助设计人员以调用数据 模板的方式进行芯片设计,大大减少了工程师所耗费的时间和精力投入。

同时,单元库还 能够帮助进行设计的移植。单元库的出现,使得半导体的设计思路得以抽象化。工程师可 以从一个更高的层次进行设计,即直接采用高级语言的设计电路板,并把底层细节归入到 库或者 CAE 工具中。逻辑综合推动芯片设计进入系统级。逻辑综合用于形成门级网表。逻辑综合工具诞生于 1986 年,由 Aart de Geus 发明,通过翻译、优化、映射三步,将对电路的 RTL 级描述(Register Transfer Level)转换为门级网表(Gate-Level Netlist),作为后端布线布局工具的输入文件。 逻辑综合工具推动芯片设计效率大幅提升。通过逻辑综合工具,芯片设计从手动设计电路 进入电脑语言写电路的时代,芯片设计的抽象程度与设计效率进一步提升,推动 IC 设计从 晶体管级、门级逐步进入架构级、系统级。逻辑综合技术随芯片设计复杂度提升而进步。物理综合加入:随着半导体工艺进入纳米级 (40nm 以下),连线的延时难以忽略,版图布局规划信息被加入这一环节,一方面可以估 算连线延时,另一方面还可以对布线拥堵情况进行预测及优化,代表产品如 2004 年推出的 Design Compiler Graphical。分布式综合技术加入:随着人工智能、5G 等新型技术应用逐 步展开,对芯片性能的需求也不断提升,EDA 方法面对的数据集愈发庞大,并行计算有助 于加速 EDA 算法执行,代表产品如 Design Compiler NXT。

标签: TMT行业报告

相关文章

根据伽马数据和游戏工委联合发布的《中国游戏产业报告》数据,2024 年国内游戏市场规 模约 3257.83 亿元,同比增长 7.53%,用户规模约 6...

2025-04-18 12 TMT行业报告

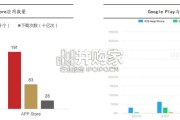

安卓系统开源的生态和商业模式决定了其对应用程序的限制必定远少于iOS,也更加多元化。根据苹果的规定,所有适用于iOS的应用 程序需通过苹果审核,并进行...

2025-04-11 35 TMT行业报告

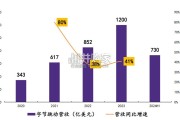

从2020至2024年数据来看,移动互联网月总独立设备数环比虽有增长,但整体增速缓慢;用户单日使用时间及次数同比增长率也呈 现波动下降趋势,表明流量红...

2025-04-09 45 TMT行业报告

产业链上游,测试仪器所需要的各类元器件和零部件中,除极少部分关键芯片和高性能原材料掌握在 少数几家国外企业外,大多数均为常规的、生产量大、价格稳定的电...

2025-04-07 29 TMT行业报告

商业本质是增长,2012~2019年,移动互联网时代字节跳动通过渐进式创新实现主业快速增长,在夯实主业同时通过外延等方 式切入新赛道助力后续业务新增长...

2025-03-18 129 TMT行业报告

游戏云是游戏科技的重要组成,聚焦于服务各类游戏业务及游戏衍生业务场景的云基础设施及云能力平台。游戏云将游戏领域不同 业务场景所需基础能力(包括以计算、...

2025-03-18 35 TMT行业报告

最新留言